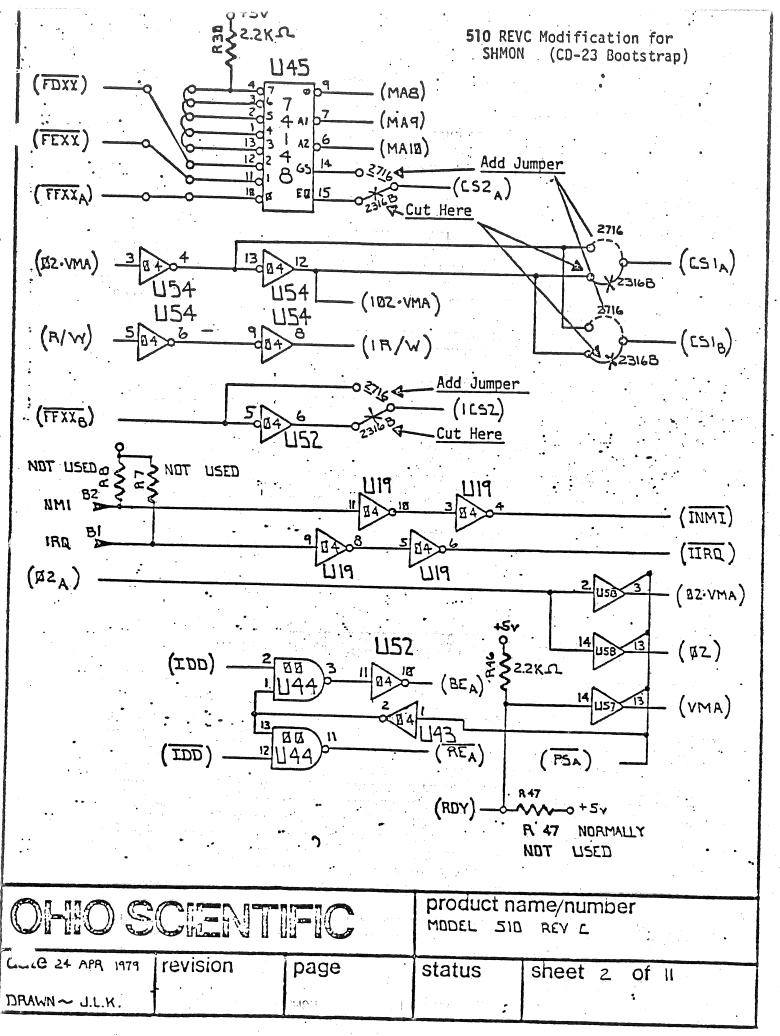

It has come to our attention that many of you are not aware of the changes to the 510 CPU Board. We are currently shipping revision C of the 510 Board. The main difference between revision C and Revision B is the fact the 1702 support Eproms have been replaced by one support masked ROM (2316). This normally has no effect on the system with but two exceptions. The first exception is with respect to the CD-74 Hard Disc. Formally a 65H Hard Disc-Bootstrap Eprom was a required addition to any system desiring to boot directly from the hard disc. Now due to the masked ROM, the CD-74 Bootstrap routine is already on the board and is ready to go. However, the same bootstrap routine will not work for the CD-23. Therefore, one must replace the support ROM on the REV C Board with a SHMON 2758 Eprom. The revision B 510 Board requires the 65H-23 1702 Hard Disc bootstrap Eprom when used with the CD-23 Hard Disc. When placing orders for CD-23 Hard Discs, please include information specifying what revision of the 510 Board the CD-23 is to be used with. The table below outlines the different system configurations:

## 510 Revision B:

W/ CD-23 Requires 65H-23 1702 Disc Bootstrap Eprom

W/ CD-74 Requires 65H 1702 Disc Bootstrap Eprom

## 510 Revision C:

W/ CD-23 Requires SHMON 2753 support Eprom & Board changes

W/ CD-74 Requires no Board modification or extra parts

The Board modifications for the Rev C CD-23 are shown in the enclosed Schematic.

Creating 'Data File(s) Only' Diskettes Under OS-65U

OS-65U has two requirements for any diskette intended to be a 'Data File(s) Only' Diskette. The requirements are:

1) System must reside on diskette

2) First entry in directory must be 'DIREC\*'

The System must reside on the diskette due to the fact that the copier program calls a page of code from the system portion of the diskette it is copying from. The reason that DIREC\* must be the first entry is that this entry defines the location and size of the directory. The proper steps for the creation of a 'Data File(s) Only' Diskette are listed below:

- Run 'Copier' and initialize the 'Data File(s) Only' Diskette from 0 to 275967

- 2) Copy the System portion of OS-65U to the 'Data File(s) Only' Diskette

- 3) Using 'Create' create an entry on the 'Data File(s) Only' Diskette as follows:

6 11

- B) Files Length = 1000 C) File Type = OTHER (0) D) Access Rights = NONE (N) E) Password = PASS

- F) After creation of the file is complete, Exit the Create Program (X) and type a Close CR.

The diskette may now be used as a 'Data File(s) Only' Diskette.

The following list contains a few memory locations and 'Pokes' of interest in OS-65U V1. 1.

Location of Control S, Q, C, O, D and W in OS-65U

| Control Code                                                | Contents                                                                   | Run Time Address                                                                                         |

|-------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Control S Control Q Control C Control O Control D Control W | 19 (\$13)<br>17 (\$11)<br>03 (\$03)<br>15 (\$0F)<br>07 (\$07)<br>23 (\$17) | 16086 (\$3ED6)<br>16096 (\$3EE0)<br>16127 (\$3EFF)<br>16131 (\$3F03)<br>16137 (\$3F09)<br>16139 (\$3F0B) |

\*\*\* POKES \*\*\*

This POKE permits one to respond with CR only in response to an input statement. String inputs return in null string and numberic inputs return the variable equal Zero.

POKE 2888, 0: REM Normally (27)

POKE to permit , and : in input statements

POKE 2972, 13: REM Permit , / Normally (58) POKE 2976, 13: REM Permit : / Normally (44)

## 520 RAM Board with Respect to Level III

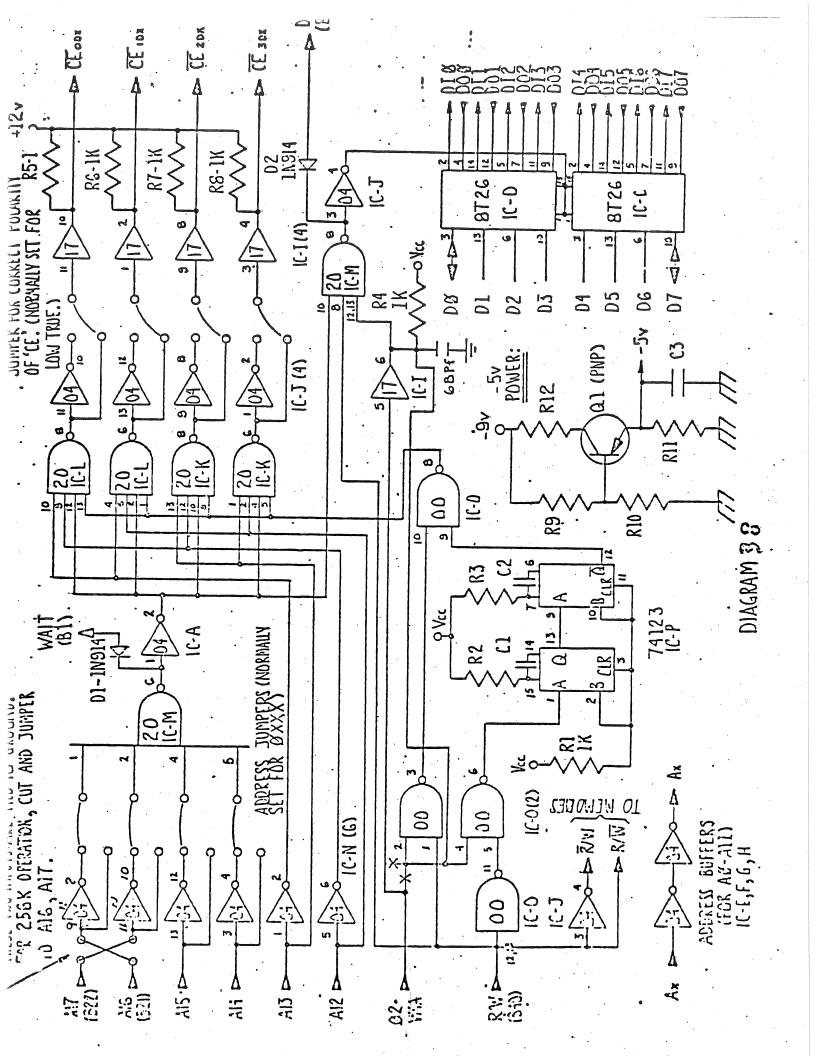

There are two corrections to the 520 Board required for its use in a Level III System. The first correction clears up noise problems on the 02\*VMA Line during D1 of the System Clock. The correction should be made to all 520 RAMS Boards except those in the base partition (Partition F). The correction re-routes 02\*VMA on its way to IC-0. 02\*VMA is modified to first go through IC-I. Pin 6 of IC-I then is fed to pins 2 and 4 of IC-I. Note that the addition of the 68 PF Cap forms a RC noise trap via R4 and the 68 PF Cap. The second correction is a correction to the original 520 Board documentation. The memory management lines

OHIO SCIENTIFIC TECH NEWS LETTER NUMBER TWO cont.

Al6 and Al7 were shown reversed. The enclosed Schematic has been corrected.

Once again, we have found ourselves in a position of issuing a fix for a fix (as does anyone who issues corrections). This fix is in reference to the Tech-News Letter Number One. In particular, this fix references the patch for the undefined user function bug. The change is simply:

· The original line read as:

000012DB 9B ? D4

The corrected line should read:

000012DB 9B ? DO

Use of 520 Memory Board in Level III Systems

To use 520 memory boards in Level III systems two changes re required. One is to address the memory boards for each partition and the other is to perform modifications to all 520 memory boards, except those at Partition F, to eliminate possible noise problems on the 02.VMA line during 01.

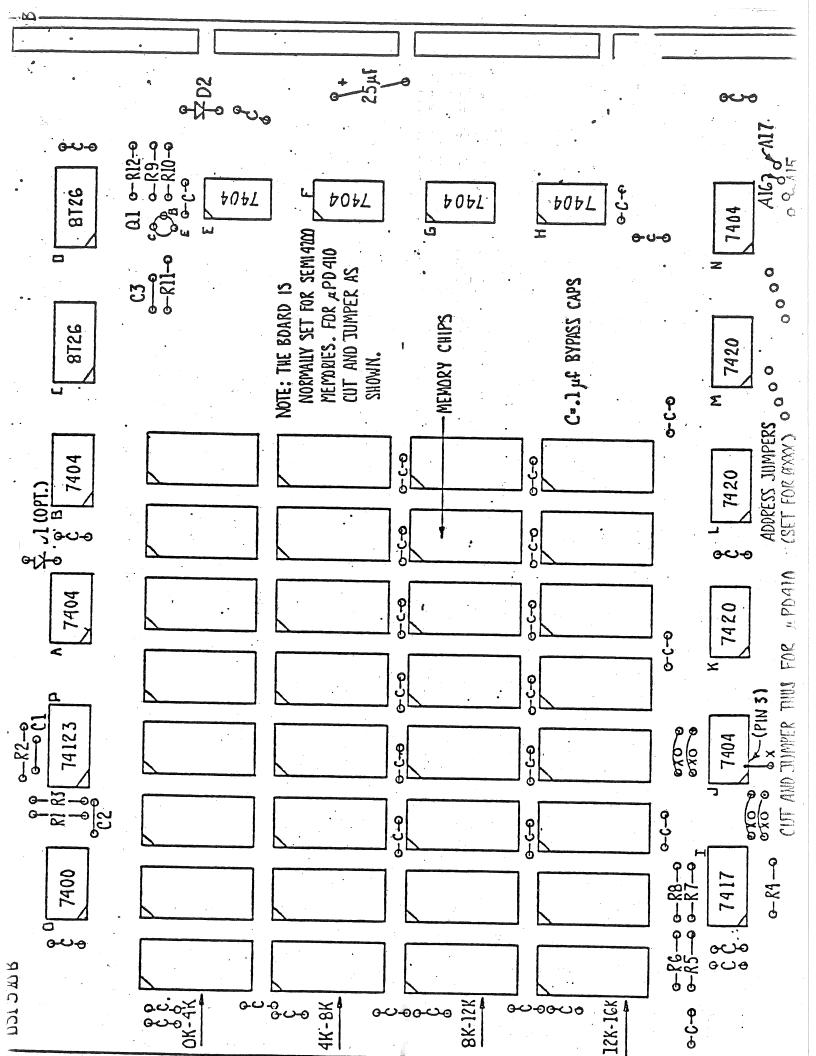

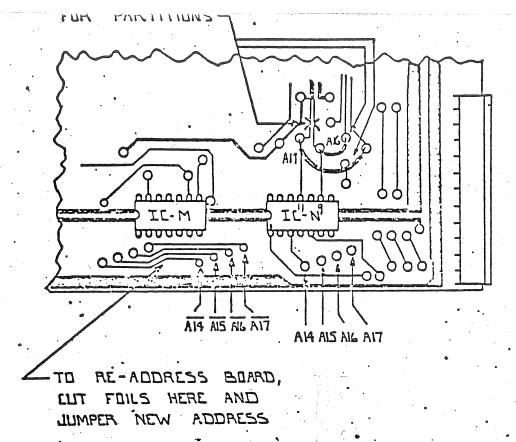

First, we will cover the addressing for multiple partitions. As 520 memory boards have only two additional addresses, A16 and A17, only four partitions may exist in a Level III system using 520 boards. Figure 35 contains the address jumpering information. Partition F will be where the main operating system resides with Partitions C, D and E being used for multiple users.

When using 520 memory boards in Level III systems, the following changes should be performed on all 520 boards except those at Partition F. The 520 boards at Partition F should be placed as close to the 510 board as possible. The recommended order in C3-B systems is as follows:

| 470 | • | Floppy Interface     |  |  |

|-----|---|----------------------|--|--|

| 510 | • | CPU                  |  |  |

| 525 |   | Dual Port            |  |  |

| 590 |   | Hard Disk Controller |  |  |

| 520 | • | Memory Board         |  |  |

| 520 |   | Memory Board         |  |  |

| 520 | • | Memory Board .       |  |  |

The remaining 520 memory boards should be placed in the front eight slots of the computer.

By placing the Partition F 520 memory boards in this order, and making the following modifications to the other 520 memory boards in the system, possible noise problems will be eliminated. Partition F is not modified so that triple processor capability is not affected. Refer to Figures 33 and 34 for sections of boards affected.

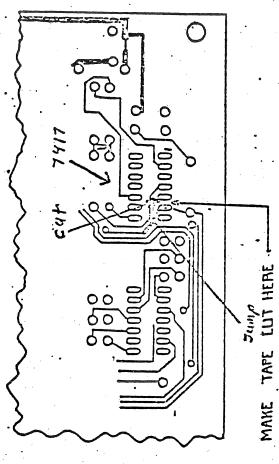

- I. Cut the tape running from Pin 5 of IC-I (7417) going to Pins 2 and 4 of IC-O (7400) as shown in Figure 36.

- II. Jumper the tape that goes to Pins 2 and 4 of IC-O (7400) to Pin 6 of IC-I (7417) as shown in Figure 36.

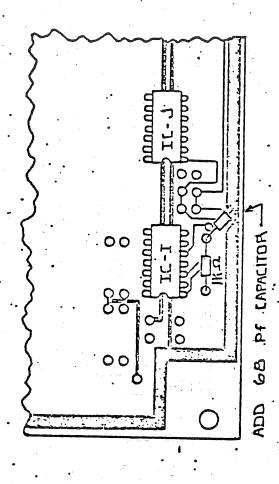

- III. Install a 68 pf capacitor on the top side of the board from R4 (1K ohm resistor) on the side connected to Pin 6 of IC-I to ground as shown in Figure 37.

This completes the modifications to the 520 memory boards.

FRONT OF 520 BOARD

DIAGRAM 33

REAR OF 520 BOARD

DIAGRAM 34

cut foil run coming from pin S As stown. Than jumpen Pin 6 to Fail run just cut from pin. 5.

MODIFICATION TO REAR OF 520 BOARD FOR LISE IN LEVEL III. SYSTEMS

DIAGRAM 36

MODIFICATION TO FRONT OF 520 BOARD FOR USE IN LEVEL III SYSTEMS

DIAGRAM 37

DIAGRAM 35

| ADDRESS      | BIT CONFIGURATION. |            |          |          |

|--------------|--------------------|------------|----------|----------|

| XXXE-XXX     | A 14               | AIS        | <b>X</b> | <b>X</b> |

| 4 XXX - 7XXX | A 14               | AIS        | X.       | X        |

| XXX8-XXX8    | A 14               | A15        | K        |          |

| CXXX - FXXX  | A 14               | A15        | *        | *        |

| •            |                    | ٠.         | •        |          |

| PARTITION    |                    | •          |          | •        |

| <b>C</b> .   | X                  | <b>X</b> . | Alla     | ·        |

|              | Xı                 | X          | A16      | A17      |

| E            | X.                 | X          | A14      | A17      |

| F            | *                  | χ.         | -A16     | A17      |

X = IRRELEVANT

MODEL 520 IS NORMALLY SET FOR PARTITION C, ADDRESS DXXX-3XXX.

FOR OTHER LOCATIONS, CUT AND JUMPER AS DESIRED.

MODEL 520 - ADDRESS JUMPER INFORMATION